- 成果水平:

- 应用阶段:可以量产

- 创新形式:新产品

- 合作方式:

- 成果属性:原始创新

- 交易状态:未交易

- 所 在 地:

- 交易价格:面议

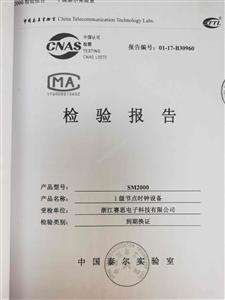

本项目的时钟发生器系列产品主要工作和成果如下: 1、采用全数字锁相环的方案,通过修改参数和调整配置产生系统 翩 8/ 需要的时钟。项目优化了算法性能,提高了锁相环的可靠性和一致性。 2、采用小数分频算法方案,可以产生需要的频率,同时在反馈回路中增加了 DTC 结构,可以更好的抑制输出时钟 spur 。 3、经中国电子技术标准化研究院赛西实验室第三方机构测试,型号KL5100A1A31AQ的5G整机用时钟发生器产品输出 rms 抖动性能优于0.15ps。 4、经国家工业信息安全发展研究中心查新,用于 PCIe 的时钟发生器的调制频率(30~33KHz)和输出 rms 抖动性能与国外主流厂商产品相当。

支持塞斯在应对国外封锁的环境中生产中国产品打造中国品牌。

1、该产品凝聚了年轻海归科研人员的爱国情怀。 2、该产品坚持自主创新,达到了国外同类产品的水平。 3、该产品可以替代进口,具有应用推广价值。

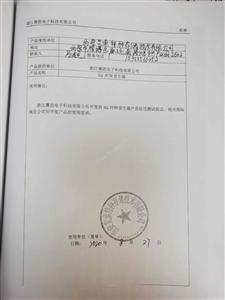

承研单位提交的《5G整机用时钟发生器系列产品评价资料汇编》内容完整。项目的创新点如下:时钟发生器采用全数字锁相环的方案,通过数字化算法,提高了锁相环的可靠性和一致性;采用改进的小数分频算法方案和增加 DTC 结构,更好抑制输出时钟毛刺。代表产品KL5100A1A3A31AQ经第三方检测,其输出 rms 抖动性能国外主流厂商产品相当。产品具有自主知识产权, KL5100A1时钟发生器达到了国外同类产品的水平,具 用推广价值。

浙江赛思电子科技有限公司自主研发了一款全数字锁相环电路,通过参数修改和调整,配置系统需要的时钟频率,在实现时钟产生方面有更大的灵活性;通过算法数字化,提高锁相环的可靠性和一致性;采用小数分频算法,并在反馈回路中引入 DTC 结构,抑制了输出时钟的频谱毛刺。测试表明,产品的输出时钟的抖动性能和国外主流厂商的产品相当。

该公司的时钟发生器采用小数分频方案和增加 DTC 结构的反馈网络相结合的创新技术,保证了产生所需的频率,很好的抑制了时钟抖动,提高了时钟发生器的性能。产品KL5100A1输出频率和抖动性能达到了国际同类产品水平,可完全满足相关应用的产品需求,实现国产替代。 建议公司加大市场推广,扩大产品市场份额。

浙江赛思电子科技有限公司自主研发的“5G整机用时钟发生器系列产品”为解决破解中国集成电路产业“卡脖子”问题提供了一点突破,具有非常重要的实际意义。 该产品完成的主要工作有: 1.采用全数字锁相环的方案,在实现时钟产生方面有更大的灵活性,通过参 数修改和调整配置产生系统需要的时钟,提高锁相环的可靠性和一致性。采用小数分频算法方案,保证产生需要的任意频率,同时更好的抑制输出2. 时钟毛刺。 3.经第三方机构检测与查新,产品性能与国外主流厂商产品相当。 产品具有自主知识产权,建议进一步扩大该技术成果的应用领域,满足 市场需求。